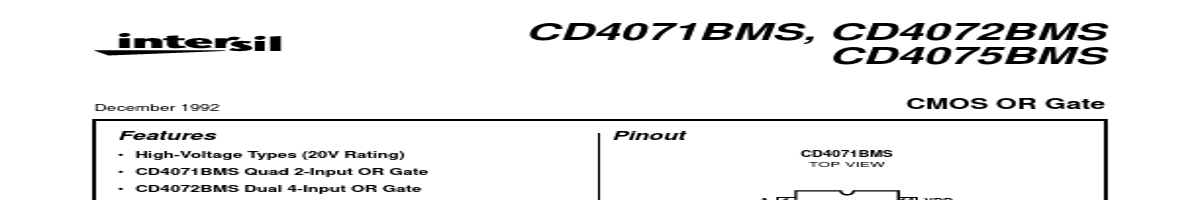

of ‘B’ Series CMOS Devices” A 1 B 2 J=A+B 3 K=C+C 4 C 5 D 6 VSS 7 14 VDD 13 H 12 G 11 M = G + H 10 L = E + F 9 F 8 E CD4072BMS TOP VIEW J=A+B+C+D 1 A 2 B 3 C 4 14 VDD 13 K = E +F + G + H 12 H 11 G 10 F 9 E 8 NC Description CD4071BMS, CD4072BMS and CD4075BMS OR gates provide the system designer with direct implementation of the positive-logic OR functio.

• High-Voltage Types (20V Rating)

• CD4071BMS Quad 2-Input OR Gate

• CD4072BMS Dual 4-Input OR Gate

• CD4075BMS Triple 3-Input OR Gate

• Medium Speed Operation: - tPHL, tPLH = 60ns (typ) at 10V

• 100% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and +25oC

• Standardized Symmetrical Output Characteristics

• Noise Margin (Over Full Package Temperature Range): - 1V at VDD = 5V - 2V at VDD = 10V - 2.5V at VDD = 15V

• 5V, 10V and 15V Parametric Ratings

• Meets All Requirements of JEDEC Tentative Standard No. 13B, “Standa.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CD4071BM |

National Semiconductor |

Quad 2-Input OR/ AND Buffered B Series Gate |

|

| 2 | CD4071B |

ETCTI |

CMOS OR GATES |

|

| 3 | CD4071B |

RCA Solid State |

(CD4071B - CD4075B) CMOS OR Gates |

|

| 4 | CD4071BC |

National Semiconductor |

Quad 2-Input OR/ AND Buffered B Series Gate |

|

| 5 | CD4071BE |

RCA Solid State |

(CD4071B - CD4075B) CMOS OR Gates |

|

| 6 | CD4071BE |

Harris Semiconductor |

CD4000 Series |

|

| 7 | CD4070B |

RCA |

CMOS Quad Exclusive-OR and Exclusive-NOR Gate |

|

| 8 | CD4070B |

ETCTI |

CMOS Quad Exclusive-OR and Exclusive-NOR Gate |

|

| 9 | CD4070B |

Harris Semiconductor |

(CD4070B / CD4077B) CMOS Quad Exclusive OR and Exclusive NOR Gate |

|

| 10 | CD4070BC |

National Semiconductor |

Quad 2-Input EXCLUSIVE-OR/ NOR Gate |

|

| 11 | CD4070BE |

Harris Semiconductor |

(CD4070B / CD4077B) CMOS Quad Exclusive OR and Exclusive NOR Gate |

|

| 12 | CD4070BM |

National Semiconductor |

Quad 2-Input EXCLUSIVE-OR/ NOR Gate |

|