The AZ10/100EL32 is an integrated ÷2 divider. The reset pin is asynchronous and is asserted on the rising edge. Upon power-up, the internal flip-flop will attain a random logic state; the reset allows for the synchronization of multiple EL32’s in a system. The EL32 provides a VBB output for single-ended use or a DC bias reference for AC coupling to the devic.

•

•

•

•

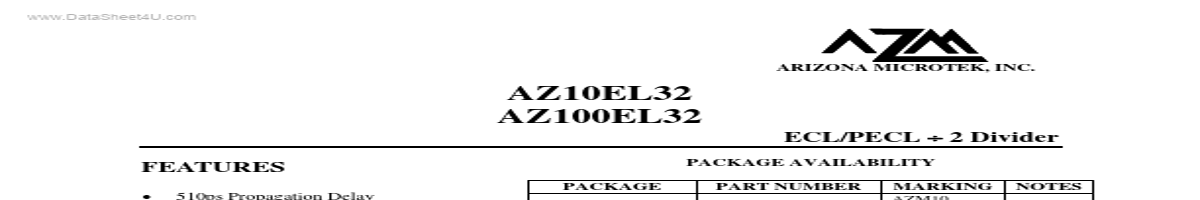

• PACKAGE 510ps Propagation Delay 3.0GHz Toggle Frequency High Bandwidth Output Transitions 75kΩ Internal Input Pulldown Resistors Direct Replacement for ON Semiconductor MC10EL32 & MC100EL32

SOIC 8 SOIC 8 SOIC 8 RoHS Compliant / Lead (Pb) Free TSSOP 8 TSSOP 8

1 2

ECL/PECL ÷ 2 Divider

PACKAGE AVAILABILITY PART NUMBER

AZ10EL32D AZ100EL32D AZ100EL32D+ AZ10EL32T AZ100LVEL32T

MARKING

AZM10 EL32 AZM100 EL32 AZM100+ EL32 AZT EL32 AZH EL32

NOTES

1,2 1,2 1,2 1,2 1,2

Add R1 at end of part number for 7 inch (1K parts), R2 for 13 inch (2.5K parts) Tape & Reel. Date code format: “Y” or “YY” f.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | AZ100EL31 |

Arizona |

ECL/PECL D Flip-Flop |

|

| 2 | AZ100EL01 |

Arizona Microtek |

ECL/PECL 4-Input OR/NOR |

|

| 3 | AZ100EL07 |

Arizona |

ECL/PECL 2-Input XOR/XNOR |

|

| 4 | AZ100EL11 |

Arizona |

ECL/PECL 1:2 Differential Fanout Buffer |

|

| 5 | AZ100EL16 |

Arizona Microtek |

ECL/PECL Differential Receiver |

|

| 6 | AZ100EL16VO |

AZM |

ECL/PECL Oscillator Gain Stage and Buffer |

|

| 7 | AZ100EL16VS |

Arizona |

ECL/PECL Differential Receiver |

|

| 8 | AZ100EL58 |

Arizona Microtek |

ECL/PECL 2:1 Multiplexer |

|

| 9 | AZ100ELT20 |

Arizona |

CMOS/TTL to Differential PECL Translator |

|

| 10 | AZ100ELT21 |

Arizona |

Differential PECL to CMOS/TTL Translator |

|

| 11 | AZ100ELT22 |

Arizona Microtek |

CMOS/TTL to Differential PECL Translator |

|

| 12 | AZ100ELT23 |

Arizona |

Dual Differential PECL to CMOS/TTL Translator |

|