Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

.... 3 SHARC Processor .... 4 SHARC+ Core Architecture ...... 6 System Infrastructure 8 System Memory Map 8 Security Features ........

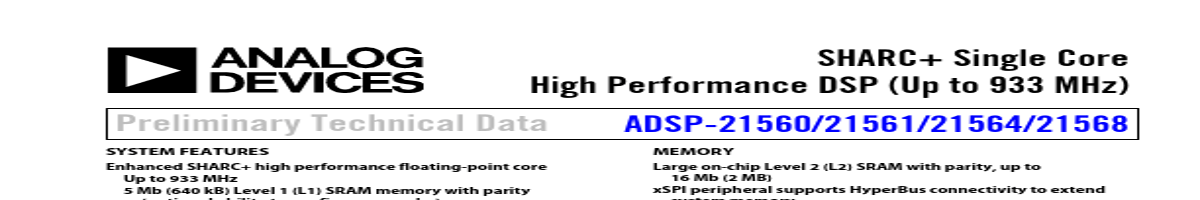

Enhanced SHARC+ high performance floating-point core Up to 933 MHz 5 Mb (640 kB) Level 1 (L1) SRAM memory with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point Byte, short word, word, long word addressed Powerful DMA system On-chip memory protection Integrated safety features 17 mm × 17 mm, 400-ball CSP_BGA (0.8 mm pitch), RoHS compliant 120-lead LQFP_EP (0.4 mm pitch), RoHS compliant Low system power across automotive temperature range 3.3 V I/O with no power sequencing requirement ADSP-21560/21561/21564/21568 MEMORY Large o.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | ADSP-21560 |

Analog Devices |

SHARC+ Single Core High Performance DSP |

|

| 2 | ADSP-21561 |

Analog Devices |

SHARC+ Single Core High Performance DSP |

|

| 3 | ADSP-21564 |

Analog Devices |

SHARC+ Single Core High Performance DSP |

|

| 4 | ADSP-21566 |

Analog Devices |

High Performance DSP |

|

| 5 | ADSP-21567 |

Analog Devices |

High Performance DSP |

|

| 6 | ADSP-21569 |

Analog Devices |

High Performance DSP |

|

| 7 | ADSP-21571 |

Analog Devices |

SHARC+ Dual-Core DSP |

|

| 8 | ADSP-21573 |

Analog Devices |

SHARC+ Dual-Core DSP |

|

| 9 | ADSP-21583 |

Analog Devices |

SHARC+ Dual-Core DSP |

|

| 10 | ADSP-21584 |

Analog Devices |

SHARC+ Dual-Core DSP |

|

| 11 | ADSP-21587 |

Analog Devices |

SHARC+ Dual-Core DSP |

|

| 12 | ADSP-2100A |

Analog Devices |

DSP Microcomputers |

|