The AD6459 is a 3 V, low power receiver IF subsystem for operation at input frequencies as high as 500 MHz and IFs from 5 MHz up to 50 MHz. It is optimized for operation in GSM, DCS1800 and PCS1900 receivers. It consists of a mixer, an IF amplifier, I and Q demodulators, a phase-locked quadrature oscillator, a precise AGC subsystem, and a biasing system wit.

Fully Compliant with Standard and Enhanced GSM Specification

–11 dBm Input 1 dB Compression Point 0 dBm Input Third Order Intercept 10 dB SSB Noise Figure (50 ⍀) DC-500 MHz RF and LO Bandwidths Linear IF Amplifier Linear-in-dB and Stable over Temperature Voltage Gain Control Quadrature Demodulator On-Board Phase-Locked Quadrature Oscillator Demodulates IFs from 5 MHz to 50 MHz Low Power 8 mA at Midgain 2 A Sleep Mode Operation 2.7 V to 5.5 V Operation Interfaces to AD7013, AD7015 and AD6421 Baseband Converters 20-Lead SSOP

GSM 3 V Receiver IF Subsystem AD6459

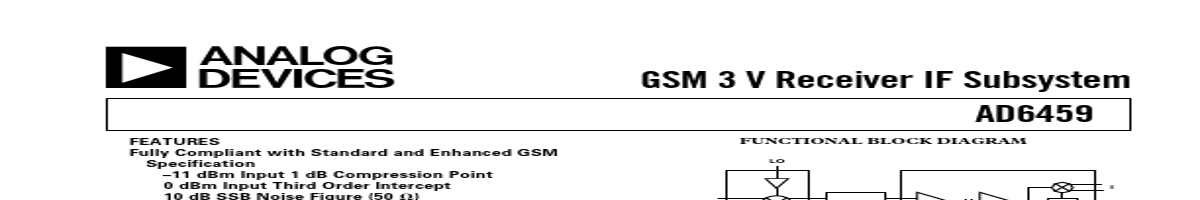

FUNCTIONAL BLOCK DIAGRAM

LO I RF.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | AD645 |

Analog Devices |

Low Noise/ Low Drift FET Op Amp |

|

| 2 | AD6458 |

Analog Devices |

GSM 3 V Receiver IF Subsystem |

|

| 3 | AD640 |

Analog Devices |

DC-Coupled Demodulating 120 MHz Logarithmic Amplifier |

|

| 4 | AD6402 |

Analog Devices |

IF Transceiver Subsystem |

|

| 5 | AD641 |

Analog Devices |

250 MHz Demodulating Logarithmic Amplifier |

|

| 6 | AD6411 |

Analog Devices |

DECT RF Transceiver |

|

| 7 | AD642 |

Analog Devices |

Precision/ Low Cost Dual BiFET Op Amp |

|

| 8 | AD6426 |

Analog Devices |

Enhanced GSM Processor |

|

| 9 | AD6432 |

Analog Devices |

GSM 3 V Transceiver IF Subsystem |

|

| 10 | AD6439 |

Analog Devices |

Discrete Multitone (DMT) Coprocessor |

|

| 11 | AD644 |

Analog Devices |

Dual High Speed/ Implanted BiFET Op Amp |

|

| 12 | AD6440 |

Analog Devices |

Analog Front-End |

|