of Intel’s thermal impedance test methodology. ~“52’80320NL’ ~ T2 L { I’__”llT2EX PI.’ P1.1 P1.2 P1.3 P1.4 P1.5 P1,6 1 2 3 4 5 6 7 40 Vcc 39 P’,’ ADO 38 PO.1AD1 37 PO.2A02 36 PO.3 A03 35 PO.4AD4 34 PO.5AD5 PI.6 ::8:; P1.7 6 33 P06 AD’ ‘1RST RU2 P3.O TXD P3.1 INTO P3.2 INT1 P3,3 TOP3 4 11 P3.5 ~ P3.6 t% P3.7 9 10 11 12 13 14 15 16 17 3 PO.7A07 3 EI.

of the MCS 51 Family, as listed below: Port Pin P3,0 P3.1 P3.2 P3,3 P3.4 P3.5 P3.6 P3.7 Alternative Function RXD (serial input port) TXD (serial output port) INTO(external interrupt O) INT1 (external interrupt 1) TO(Timer Oexternal input) T1 (Timer 1 external input) WR (external data memory write strobe) ~ (external data memory read strobe) RST: Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device, ALE/PROG: Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the p.

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

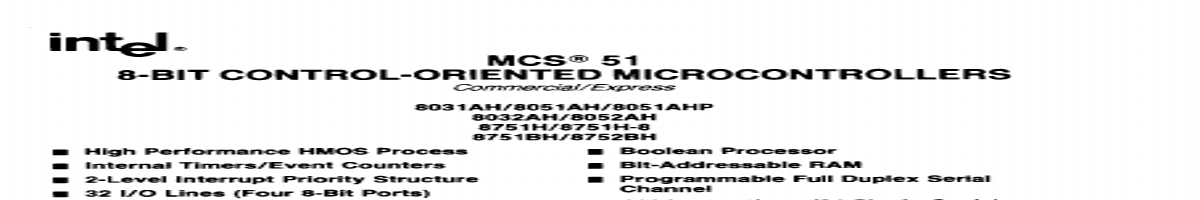

| 1 | 8751H |

Intel Corporation |

MCS51 8-BIT CONTROL-ORIENTED MICROCONTROLLERS |

|

| 2 | 8751BH |

Intel Corporation |

MCS 51 8-BIT CONTROL-ORIENTED MICROCONTROLLERS |

|

| 3 | 8752BH |

Intel Corporation |

MCS 51 8-BIT CONTROL-ORIENTED MICROCONTROLLERS |

|

| 4 | 8755A |

Intel Corporation |

16/384-BIT EPROM WITH I/O |

|

| 5 | 87002-02 |

IDT |

Differential-to-LVCMOS/LVTTL Zero Delay Clock Generator |

|

| 6 | 87016I |

Renesas |

LVCMOS/LVTTL Clock Generator |

|

| 7 | 8705I |

IDT |

Differential-to-LVCMOS/LVTTL Clock Generator |

|

| 8 | 87196CA |

Intel Corporation |

ADVANCED 16-BIT CHMOS MICROCONTROLLER |

|

| 9 | 87196CB |

Intel Corporation |

ADVANCED 16-BIT CHMOS MICROCONTROLLER |

|

| 10 | 8724E |

Maxim Integrated Products |

MAX8724E |

|

| 11 | 87267-2450 |

Molex |

(87267-xxxx) HEADER CONNECTOR |

|

| 12 | 87267-xxxx |

Molex |

(87267-xxxx) HEADER CONNECTOR |

|