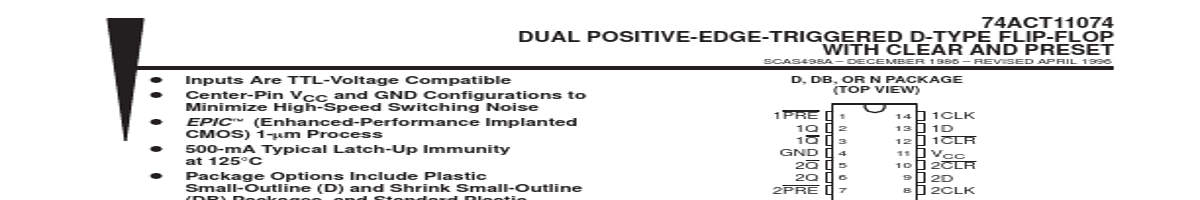

This device contains two independent positive-edge-triggered D-type flip-flops. A low level at the preset (PRE) or clear (CLR) input sets or resets the outputs regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup-time requirements are transferred to the outputs on the low-to-high tra.

se. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold time interval, data at the D input may be changed without affecting the levels at the outputs.

The 74ACT11074 is characterized for operation from

–40°C to 85°C.

FUNCTION TABLE

INPUTS

OUTPUTS

PRE CLR CLK D

Q

Q

L

H

X

X

H

L

H

L

X

X

L

H

L

L

X

X

H{ H{

H

H

↑

H

H

L

H

H

↑

L

L

H

H

H

L

X

Q0 Q0

† This configuration is unstable; that is, it does not

persist when either PRE or CLR returns to its

inactive (high) level.

Please be aware .

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | 74ACT11000 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-NAND GATES |

|

| 2 | 74ACT11002 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-NOR GATES |

|

| 3 | 74ACT11004 |

Texas Instruments |

HEX INVERTER |

|

| 4 | 74ACT11008 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-AND GATE |

|

| 5 | 74ACT11010 |

Texas Instruments |

Triple 3-Input Positive-NAND Gates |

|

| 6 | 74ACT11011 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-AND GATES |

|

| 7 | 74ACT11014 |

Texas Instruments |

Hex Schmitt-Trigger Inverter |

|

| 8 | 74ACT11021 |

Texas Instruments |

DUAL 4-INPUT POSITIVE-AND GATES |

|

| 9 | 74ACT11027 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NOR GATES |

|

| 10 | 74ACT11030 |

Texas Instruments |

8-INPUT POSITIVE-NAND GATES |

|

| 11 | 74ACT11032 |

Texas Instruments |

QUADRUPLE 2-INPUT POSITIVE-OR GATES |

|

| 12 | 74ACT11034 |

Texas Instruments |

Hex Noninverters |

|