|

Features

|

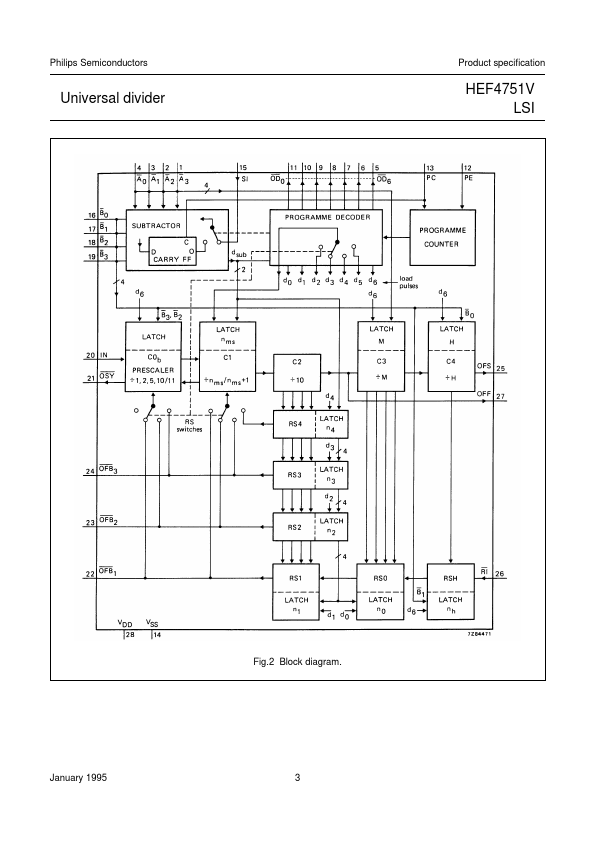

of a single U.D. The U.D. provides a fast output signal FF at output OFF, which can have a phase jitter of ± 1 system input period, to allow fast frequency locking. The slow output signal FS at output OFS, which is jitter-free, is used for fine phase control at a lower speed.

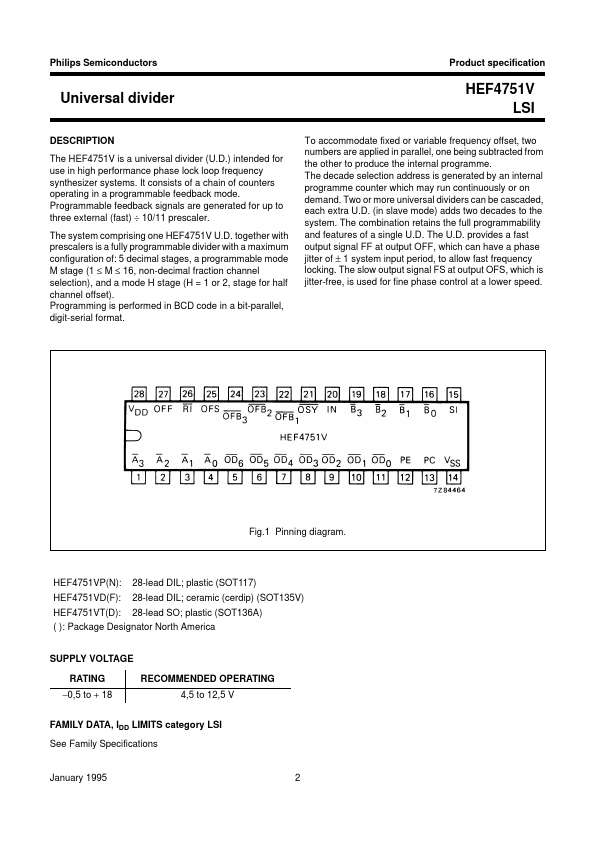

Fig.1 Pinning diagram.

HEF4751VP(N): HEF4751VD(F): HEF4751VT(D):

28-lead DIL; plastic (SOT117) 28-lead DIL; ceramic (cerdip) (SOT135V) 28-lead SO; plastic (SOT136A)

( ): Package Designator North America SUPPLY VOLTAGE RATING −0,5 to + 18 RECOMMENDED OPERATING 4,5 to 12,5 V

FAMILY DATA, IDD LIMITS category LSI See Fam...

|