Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

PI7C8150B |

| Part Number | PI7C8150B |

| Manufacturer | Pericom Semiconductor Corporation |

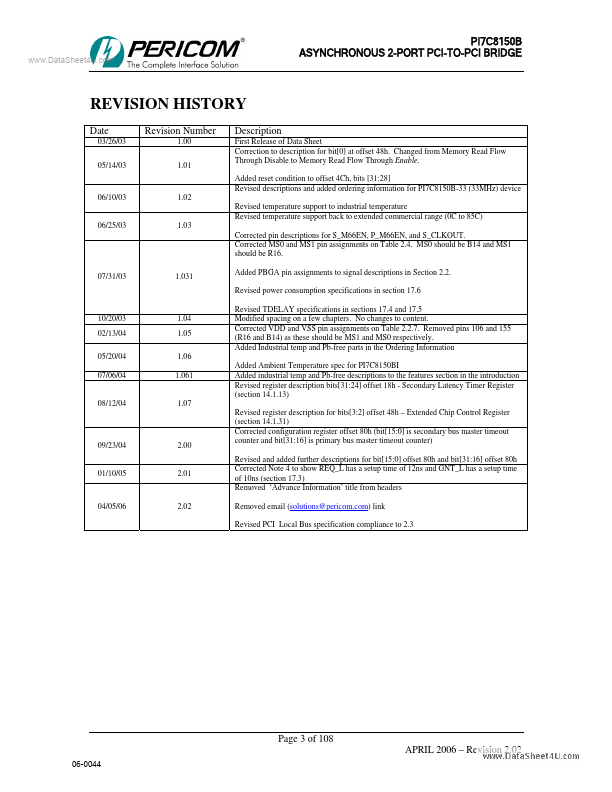

| Description | First Release of Data Sheet Correction to description for bit[0] at offset 48h. Changed from Memory Read Flow Through Disable to Memory Read Flow Through Enable. Added reset condition to offset 4Ch, b... |

| Features |

section in the introduction Revised register description bits[31:24] offset 18h - Secondary Latency Timer Register (section 14.1.13) Revised register description for bits[3:2] offset 48h – Extended Chip Control Register (section 14.1.31) Corrected configuration register offset 80h (bit[15:0] is secondary bus master timeout counter and bit[31:16] is primary bus master timeout counter) Revised and added further descriptions for bit[15:0] offset 80h and bit[31:16] offset 80h Corrected Note 4 to show REQ_L has a setup time of 12ns and GNT_L has a setup time of 10ns (section 17.3) Removed ‘Advance ... |

| Document |

PDF 2.75MB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | PI7C8150 |

Pericom Semiconductor |

2-Port PCI-to-PCI Bridge |

|

| 2 | PI7C8150A |

Pericom Semiconductor |

2-PORT PCI-to-PCI BRIDGE |

|

| 3 | PI7C8152A |

Pericom Semiconductor |

2-Port PCI-to-PCI Bridge |

|

| 4 | PI7C8152B |

Pericom Semiconductor |

2-Port PCI-to-PCI Bridge |

|

| 5 | PI7C8154A |

Pericom Semiconductor |

2-Port PCI-to-PCI Bridge |

|