Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

MPC8555E |

| Part Number | MPC8555E |

| Manufacturer | Motorola Semiconductor |

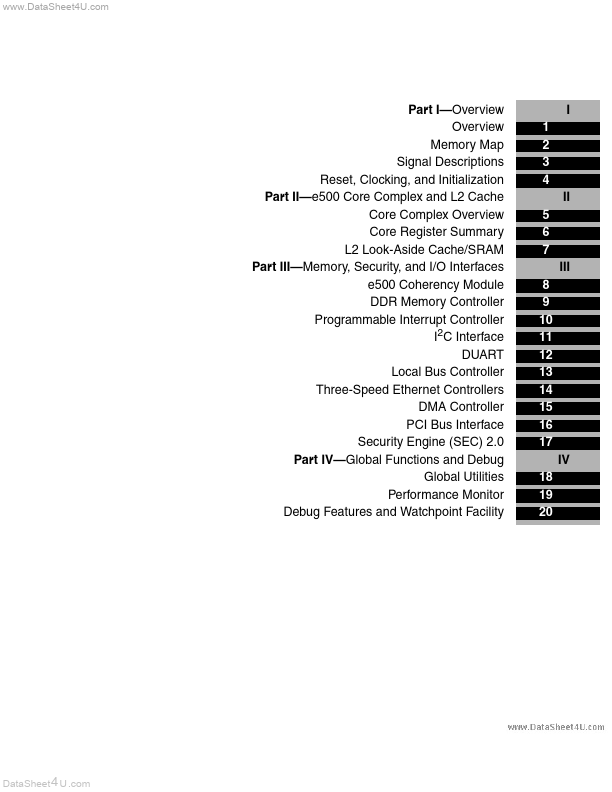

| Description | Reset, Clocking, and Initialization Part II—e500 Core Complex and L2 Cache Core Complex Overview Core Register Summary L2 Look-Aside Cache/SRAM Part III—Memory, Security, and I/O Interfaces e500 Cohe... |

| Features |

and Watchpoint Facility

I 1 2 3 4 II 5 6 7 III 8 9 10 11 12 13 14 15 16 17 IV 18 19 20

DataSheet 4 U .com

www.DataSheet4U.com

I 1 2 3 4 II 5 6 7 III 8 9 10 11 12 13 14 15 16 17 IV 18 19 20

Part I—Overview Overview Memory Map Signal Descriptions Reset, Clocking, and Initialization Part II—e500 Core Complex and L2 Cache Core Complex Overview Core Register Summary L2 Look-Aside Cache/SRAM Part III—Memory, Security, and I/O Interfaces e500 Coherency Module DDR Memory Controller Programmable Interrupt Controller I2C Interface DUART Local Bus Controller Three-Speed Ethernet Controllers DMA Cont... |

| Document |

PDF 19.53MB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | MPC855 |

Motorola |

Family Hardware Specifications |

|

| 2 | MPC850 |

Sipex Corporation |

Connecting SP5301 to MPC850 PowerQUICC |

|

| 3 | MPC850 |

Motorola |

Communications Controller Hardware Specifications |

|

| 4 | MPC852T |

Motorola |

COMMUNICATIONS CONTROLLER |

|

| 5 | MPC8533E |

Freescale Semiconductor |

PowerQUICC III Integrated Processor |

|