Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

TM50S116T |

| Part Number | TM50S116T |

| Manufacturer | ETC |

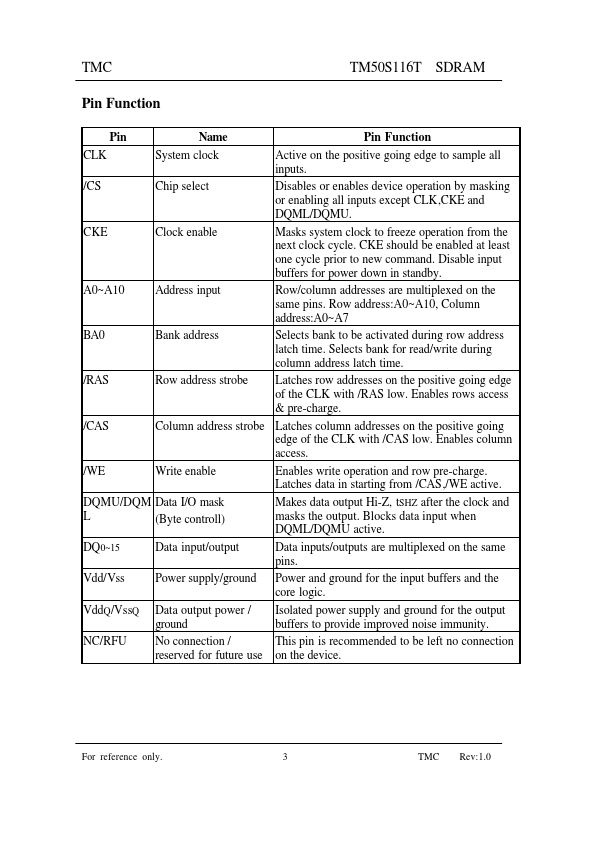

| Description | TM50S116T SDRAM The TM50S116T is organized as 2-bank x 524288-word x 16-bit(1Mx16), fabricated with high performance CMOS technology. Synchronous design allows precise cycle control with the use of ... |

| Features |

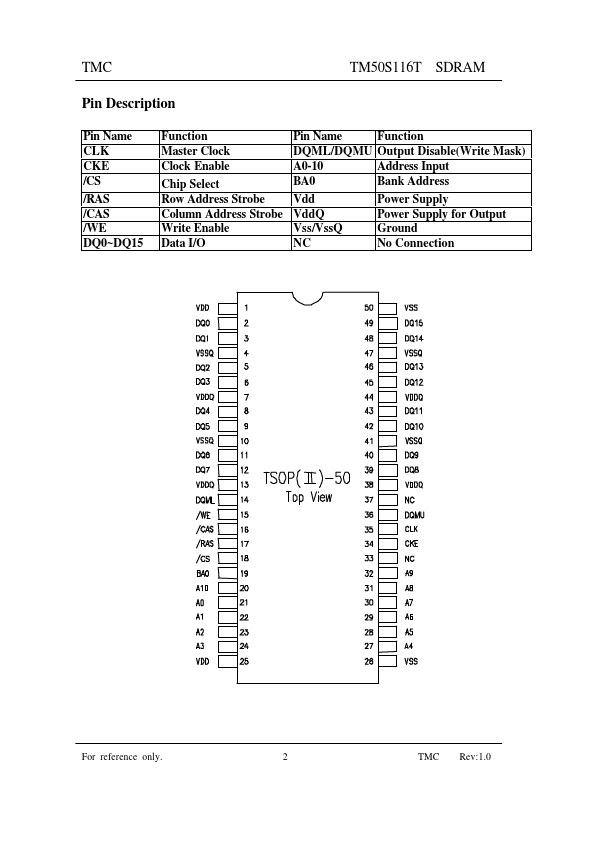

n Package 400-mil 50-pin TSOP(II) n JEDEC PC133/PC100 compatible n Single 3.3V Power Supply n LVTTL Signal Compatible n Byte control(DQML and DQMU) n Auto and Self Refresh n 64ms refresh period (4K cycles) n 11-Row x 8-Column organization n 2-Bank operation controlled by BA0 n Programmable n Pin33 and 37 are “No Connected” - CAS Latency (3 or 2 clocks) n Fully synchronous operation referenced - Burst Length (1,2,4,8 & full page) to clock rising edge - Burst type (Sequential & Interleave) n Burst read/write and burst read/single write operations capability

Frequency vs. AC Parameter

Symbol tCK... |

| Document |

PDF 93.32KB |

| Distributor | Stock | Price | Buy |

|---|