Recherchez avec le numéro de pièce ainsi que le fabricant ou la description

CY7C2262XV18 |

| Part Number | CY7C2262XV18 |

| Manufacturer | Cypress Semiconductor |

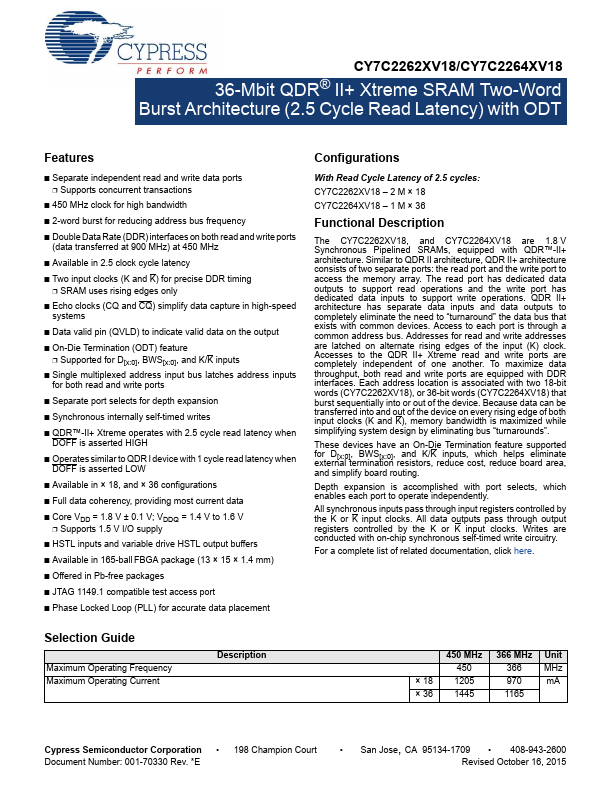

| Description | CY7C2262XV18/CY7C2264XV18 36-Mbit QDR® II+ Xtreme SRAM Two-Word Burst Architecture (2.5 Cycle Read Latency) with ODT 36-Mbit QDR® II+ Xtreme SRAM Two-Word Burst Architecture (2.5 Cycle Read Latency) ... |

| Features |

■ Separate independent read and write data ports ❐ Supports concurrent transactions ■ 450 MHz clock for high bandwidth ■ 2-word burst for reducing address bus frequency ■ Double Data Rate (DDR) interfaces on both read and write ports (data transferred at 900 MHz) at 450 MHz ■ Available in 2.5 clock cycle latency ■ Two input clocks (K and K) for precise DDR timing ❐ SRAM uses rising edges only ■ Echo clocks (CQ and CQ) simplify data capture in high-speed systems ■ Data valid pin (QVLD) to indicate valid data on the output ■ On-Die Termination (ODT) feature ❐ Supported for D[x:0], BWS[x:0], and ... |

| Document |

PDF 647.92KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Partie # | Fabricant | Description | Fiche Technique |

|---|---|---|---|---|

| 1 | CY7C2263KV18 |

Cypress Semiconductor |

36-Mbit QDR II+ SRAM Four-Word Burst Architecture |

|

| 2 | CY7C2263XV18 |

Cypress Semiconductor |

36-Mbit QDR II+ Xtreme SRAM Four-Word Burst Architecture |

|

| 3 | CY7C2264XV18 |

Cypress Semiconductor |

36-Mbit QDR II+ Xtreme SRAM Two-Word Burst Architecture |

|

| 4 | CY7C2265KV18 |

Cypress Semiconductor |

36-Mbit QDR II+ SRAM Four-Word Burst Architecture |

|

| 5 | CY7C2265XV18 |

Cypress Semiconductor |

36-Mbit QDR II+ Xtreme SRAM Four-Word Burst Architecture |

|