|

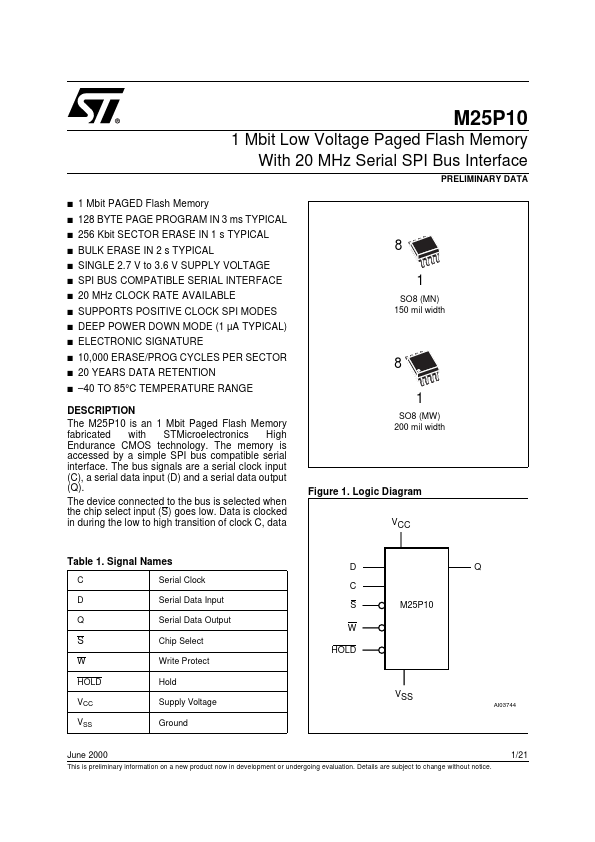

Features

|

of the device are summarized in Table 3.

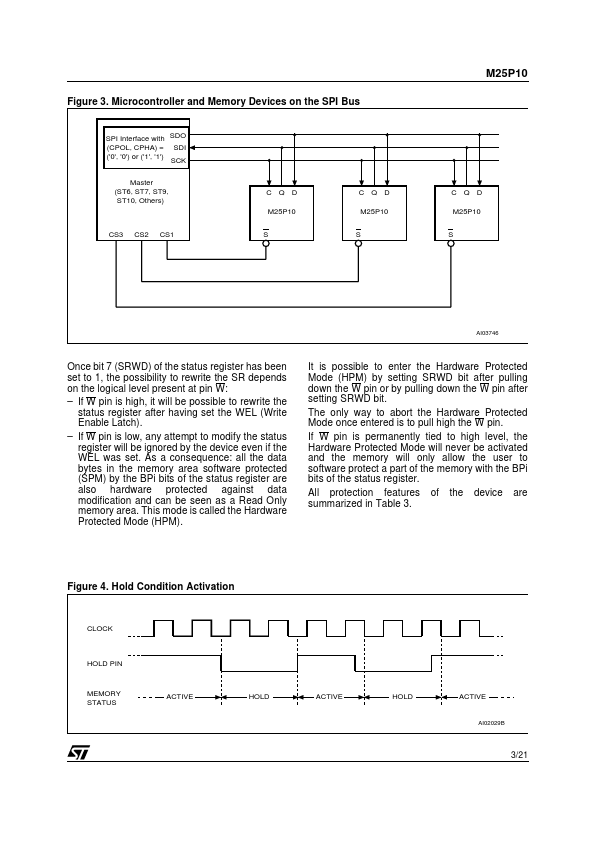

Figure 4. Hold Condition Activation

CLOCK

HOLD PIN

MEMORY STATUS

ACTIVE

HOLD

ACTIVE

HOLD

ACTIVE

AI02029B

3/21

M25P10

Figure 5. M25P10-Compatible SPI Modes

CPOL CPHA

00

C

11

C

D or Q

MSB

LSB

AI01438

Clock Polarity (CPOL) and Clock Phase (CPHA) with SPI Bus

As shown in Figure 5, the M25P10 can be driven by a microcontroller with its SPI peripheral running in either of the two following modes: (CPOL, CPHA) = (’0’, ’0’) or (CPOL, CPHA) = (’1’, ’1’). For these two modes, input data is latched in by the low to high transition of clock C, and...

|