IDT5V927 डेटा पत्रक PDF( Datasheet डाउनलोड )

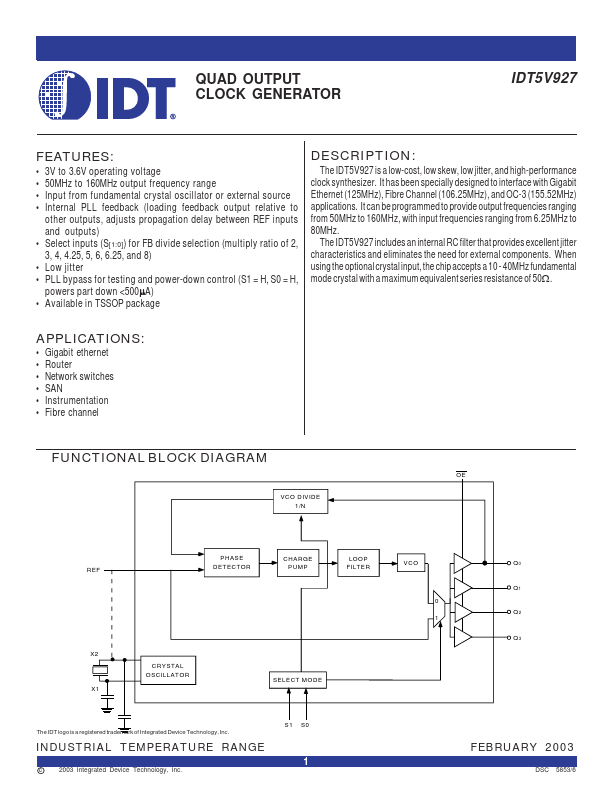

डेटा पत्रक - Quad Output Clock Generator - IDT

| भाग संख्या | IDT5V927 | |

| समारोह | Quad Output Clock Generator | |

| मैन्युफैक्चरर्स | IDT | |

| लोगो |  |

|

| पूर्व दर्शन | ||

| डाउनलोड | [ IDT5V927 Datasheet.PDF ] | |

शेयर लिंक

अनुशंसा डेटापत्रक

| भाग संख्या | विवरण | विनिर्माण |

| IDT5V926 | SINGLE OUTPUT CLOCK GENERATOR | Integrated Device |

| IDT5V927 | Quad Output Clock Generator | IDT |

www.DataSheet.in | 2017 | संपर्क | खोज | English |